深入骨髓的大变革!Intel Skylake架构完全解析

- 来源:驱动之家

- 作者:liyunfei

- 编辑:liyunfei

8月初,Intel正式发布了新一代i7-6700K、i5-6600K,但这只能算是新家族Skylake的一点餐前开胃小菜。现在,Skylake家族开始全面登场了,架构技术细节也同时公开。一起来看看它到底改进了什么吧。

本文分为两部分,内容均来自日前的IDF 2015信息峰会,其中前半部分是研讨会上的,技术细节很详细,而后者是面向公众的,宣传性质更强。

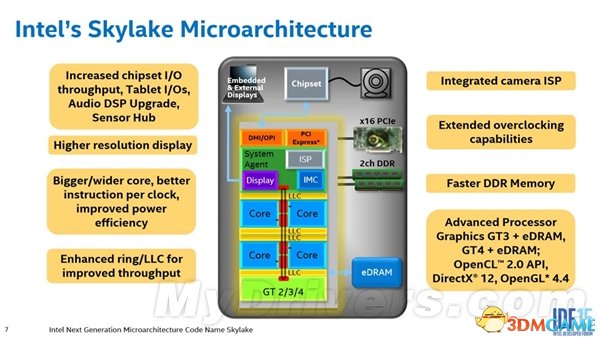

Skylake架构总图:总的来看似乎还是那一套,但几乎每个地方都相比Haswell/Broadwell做了改进。除部分包括更大更宽的核心、更高的IPC(每时钟周期指令数)、更好的电源能效、增强的环形总线/三级缓存(改进吞吐能力),当然还有开放的超频。

核显方面进化至第九代,全面支持DirectX 12、OpenCL 2.0、OpenGL 4.4,并且GT3、GT4两种级别都可选eDRAM缓存,这还是第一次,而在多媒体编解码、视频输出等方面均有增强,之前介绍过。

芯片组升级为100系列,有着更高的I/O吞吐能力、平板机I/O接口、新的音频DSP、新的传感器中心、整合的摄像头ISP,与处理器之间的通道也升级为DMI 3.0,走的是高速PCI-E 3.0。

当然了,还有主流领域第一次加入的DDR4内存,仍然是双通道。

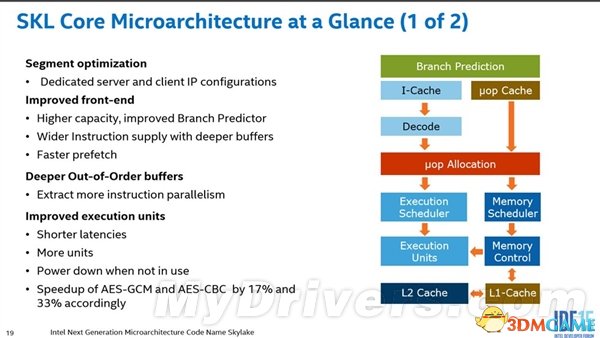

Skylake PU核心架构优化了IP布局,包括服务器和桌面。前端部分有着更大的容量、更高效分支预测器、更宽指令供应(每时钟周期6个微操作)、更深的缓冲、更快的预取,还有更深的乱序缓冲(指令并行度更高)。

执行单元部分则增多了单元、缩短了延迟、空闲时可关闭,AES-GCM、SES-CBC指令执行速度分别加快了17%、33%!

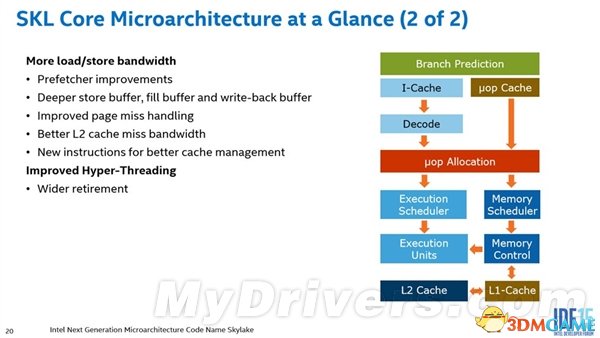

载入/存储单元的带宽也更高了,随之而来的还有改进的预取器、更深的存储/填充/写回缓冲、改进的页面丢失处理、更好的二级缓存丢失带宽、新的缓存管理指令。

玩家点评 (0人参与,0条评论)

热门评论

全部评论